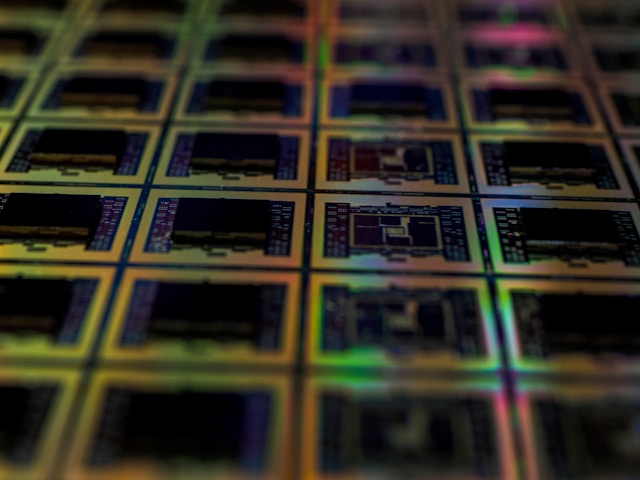

A single integrated circuit can cross four national borders between wafer start and delivery to your dock. Each crossing involves a different manufacturing stage, a different HTS classification, and potentially a different duty rate. For procurement teams managing semiconductor BOMs with hundreds of line items, cumulative tariff exposure across multi-stage supply chains is one of the most undercounted costs in electronics sourcing.

Four stages, four borders, four tariff events

The typical path for a packaged IC: wafer fabrication in Taiwan or Korea, die preparation and bumping in Japan, packaging at an OSAT in Malaysia or China, and final test either at the same OSAT or at a separate facility in Southeast Asia. Each stage adds value and each stage can trigger a tariff event depending on where the product enters customs.

US import duties apply at the point of entry into the United States. If your finished IC ships directly from a Chinese OSAT to your US facility, the full declared value of the packaged part faces whatever duty rate applies to Chinese-origin goods under its HTS code. Silicon fabricated in Taiwan, die bumped in Japan – none of it reduces the duty. Country of origin follows substantial transformation, and for most ICs the packaging step determines origin.

SEE ALSO

Section 301 tariffs on semiconductors: why country-of-origin follows the package, not the design

Two identical dies, fabricated on the same wafer at the same foundry, can carry duty rates 25 percentage points apart based solely on where they were packaged. Die A goes to Penang for packaging and enters the US at MFN rates under HTS 8542. Die B goes to Shanghai and enters at MFN plus 25% Section 301. Same wafer, same design, same electrical specifications – different tariff cost.

Classification problem compounds origin problem

Semiconductor products span multiple HTS headings depending on function and construction. Processors, memory, and logic ICs fall under different 8542 subheadings. Discrete semiconductors – diodes, transistors, thyristors – classify under 8541. Semiconductor manufacturing equipment falls under 8486. Each subheading carries its own base duty rate, and Section 301 applicability varies by list and product type.

For an OEM with a BOM containing 40 or 50 semiconductor line items, the tariff exposure calculation is not one number – it is 40 or 50 separate lookups, each requiring the correct 10-digit HTS code and the correct country of origin. Get either one wrong and the landed cost estimate is off.

We routinely see procurement teams using a single blended tariff assumption across their entire semiconductor spend. The assumption is usually based on whatever the customs broker reported on the last large shipment. This underestimates exposure on Chinese-origin parts and overestimates it on parts from duty-free origins. The net effect is a landed cost model looking reasonable in aggregate but missing the line items where tariff costs actually concentrate.

Why line-item visibility matters now

Trade policy on semiconductors has not stabilized. Section 301 tariff rates on Chinese-origin ICs have held at 25% since 2019, but exclusion windows open and close, and additional actions targeting semiconductor equipment and advanced chips continue to evolve. Companies managing tariff exposure at the BOM level – not just the shipment level – have the data to respond when policy shifts.

A *semiconductor HTS code tariff analysis* returns the current duty rate, Section 301/232 status, and country-of-origin duty comparison for any 10-digit HTS classification. Running your semiconductor line items through the lookup takes minutes and produces a line-item tariff map no blended estimate can match.

The alternative is continuing to estimate. In a market where a single OSAT decision can swing duty costs by 25 points on every unit shipped, estimates are expensive.